Планарная технология

ПЛАНАРНАЯ ТЕХНОЛОГИЯ (от англ. planar-плоский), совокупность способов изготовления полупроводниковых приборов и интегральных схем путем формирования их структур только с одной стороны пластины (подложки), вырезанной из монокристалла. Планарная технология-основа микроэлектроники, методы планарной технологии используют также для изготовления др. твердотельных приборов и устройств (напр., лазеры).

Планарная технология основывается на создании в приповерхностном слое подложки областей с разл. типами проводимости или с разными концентрациями примеси одного вида, в совокупности образующих структуру полупроводникового прибора или интегральной схемы. Преимуществ. распространение в качестве полупроводникового материала для подложек в планарной технологии получил монокристаллич. Si. В ряде случаев используют сапфир, на пов-сть к-рого наращивают гетероэпитак-сиальный слой (см. Эпитаксия)кремния п- или p-типа проводимости толщиной ок. 1 мкм. Области структур создаются локальным введением в подложку примесей (посредством диффузии из газовой фазы или ионной имплантации), осуществляемым через маску (обычно из пленки SiO2), формируемую при помощи фотолитографии. Последовательно проводя процессы окисления (создание пленки SiO2), фотолитографии (образование маски) и введения примесей, можно получить легир. область любой требуемой конфигурации, а также внутри области с одним типом проводимости (уровнем концентрации примеси) создать др. область с др. типом проводимости. Наличие на одной стороне пластины выходов всех областей позволяет осуществить их коммутацию в соответствии с заданной схемой при помощи пленочных металлич. проводников, формируемых также с помощью методов фотолитографии.

Планарная технология обеспечивает возможность одноврем. изготовления в едином технол. процессе большого числа (до неск. сотен и даже тысяч) идентичных дискретных полупроводниковых приборов или интегральных схем на одной пластине. Групповая обработка обеспечивает хорошую воспроизводимость параметров приборов и высокую производительность при сравнительно низкой стоимости изделий.

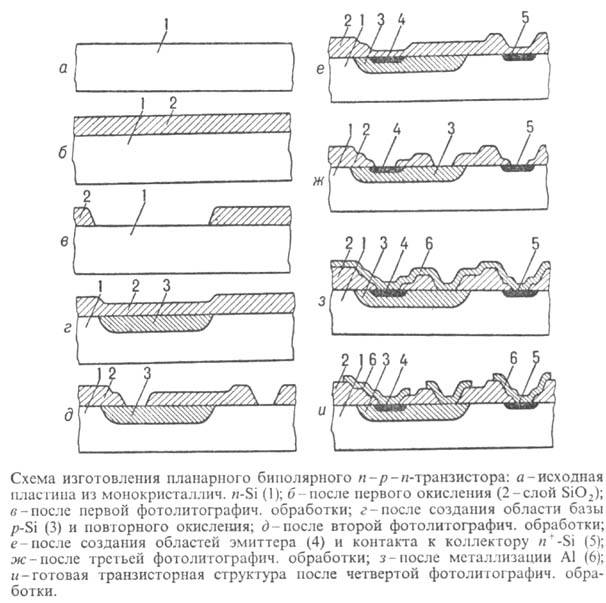

Пример изготовления биполярного n-р-n-транзистора методами планарной технологии представлен на рисунке. На подложке из монокристаллич. Si окислением получают маскирующий слой SiO2. В этом слое с помощью фотолитографии формируют окна для введения акцепторной примеси (В), в результате чего образуется базовая область транзистора (p-Si). Затем пластину снова окисляют и во вновь образованной пленке SiO2 повторной фотолитографией создают окна для формирования путем введения донорной примеси (P) эмиттерной области и контакта к коллекторной области (n + -Si). В результате цикла окисление - фотолитография вскрываются контактные окна к областям эмиттера и коллектора. На подготовленную таким образом пластину наносят (напылением вакуумным, пиролизом летучих метал-лоорг. соед. и др. способами) слой металла (чаще всего Al), из к-рого посредством фотолитографии формируют контактные площадки для присоединения металлич. выводов к соответствующим областям транзистора.

T. обр., осн. особенность планарной технологии-повторяемость однотипных операций; типовой набор операций (окисление, фотолитография и легирование), чередуясь, повторяется неск. раз. Каждая такая последовательность операций (блок) формирует определенную часть структуры: базовую или эмиттерную область, слой разводки и т.д. Изменяя число блоков, можно изготовлять любые приборы-от простых диодов (3 блока) до сложных интегральных схем (8-12 блоков). При этом осн. часть операций часто остается неизменной, а меняются только технол. режимы и шаблоны, используемые при фотолитографии.

Подложки (пластины) получают разрезкой монокристаллов Si (или др. материала) на пластины, к-рые затем шлифуют, подвергают травлению и полируют (см. Полирование), чтобы получить пов-сть без наруш. слоя. Обработанные пластины тщательно очищают хим. или плазменным (сухим) способом. Для хим. очистки применяют смеси сильных окислителей (напр., HNO3, H2O2) с к-тами (напр., с H2SO4), а также водный р-р NH3. После хим. очистки пластины промывают в деионизир. воде и сушат в центрифуге. Отмывка-одна из наиб. часто повторяющихся операций планарной технологии, при этом чистота воды имеет решающее значение. Сухая очистка в кислородной плазме применяется в осн. для удаления с пов-сти пластин оставшегося после фотолитографии фоторезиста. Плазменные процессы все шире используются в планарной технологии для очистки, травления, а также осаждения металлов и диэлектриков.

Очищенные пластины с выращенным на них эпитаксиаль-ным слоем Si или без него подвергают термич. обработке, включающей окисление, диффузию примесей или ионное легирование, отжиг пластины (в том случае, если примеси вводились ионным легированием), пиролитич. осаждение тонких пленок или их химическое осаждение из газовой фазы, геттерирование. При реализации этих процессов осуществляется формирование активных областей и др. компонентов планарных структур. Вместе с тем термич. обработка приводит к возникновению мех. напряжений в пластине, вызывает образование дефектов, перераспределение примесей в объеме пластины и в приповерхностном слое. Чтобы уменьшить отрицат. последствия, термич. обработку проводят при сравнительно невысоких т-рах (ниже 900 0C), а для ускорения процесса применяют разл. способы, напр, окисление Si проводят не в сухой, а во влажной среде при повыш. давлении. Для введения примесей все чаще вместо диффузии применяют ионное легирование (ионную имплантацию), к-рое по сравнению с диффузией обладает рядом преимуществ - универсальностью (возможность вводить практически любые в-ва в любую подложку), высокой воспроизводимостью, возможностью управлять профилем распределения примеси и изменять концентрацию вводимых примесей в широких пределах.

Пиролитически или хим. осаждением получают слои SiO2 (напр., пиролизом SiH4 в присут. O2), Si3N4 (взаимод. SiH4 или SiCl4 с NH3) и поликристаллич. Si (напр., пиролизом SiH4 в восстановит. среде)-наиб. распространенного материала для формирования затворов МОП-транзисторов (металл-оксид-полупроводник), резисторов, эмиттеров биполярных транзисторов, для изоляции компонентов интегральных схем.

По мере развития планарной технологии все большее значение приобретает геттерирование, сущность к-рого заключается в создании вне активной области структуры т. наз. стока, или геттера,-области, где р-римость загрязняющих, быстро диффундирующих, рекомбинационно-активных примесей (Au, Cu, Fe) намного выше, чем в др. областях. В результате возникает градиент концентрации примесей, к-рый обусловливает их диффузию в сторону стока. Чаще всего сток создают на обратной стороне подложки, напр. диффузией P с высокой концентрацией, мех. нарушением пов-сти подложки, легированием тяжелыми ионами с целью аморфи-зации Si, рекристаллизацией приповерхностного слоя Si под действием лазерного излучения. Геттерирование обычно проводят в конце технол. цикла или повторяют его неоднократно.

Фотолитография включает след. стадии: нанесение слоя фоторезиста на пленку SiO2, покрывающую кремниевую пластину; экспонирование слоя фоторезиста через фотошаблон-стеклянную пластину с множеством одинаковых рисунков областей прибора; проявление слоя фоторезиста; получение оксидной маски травлением пленки SiO2 через окна в проявленном фоторезисте; удаление фоторезиста. Используют фотолитографию контактную (фотошаблон контактирует со слоем фоторезиста) и проекционную, осуществляемую либо однократным проецированием фотошаблона с множеством структур на всю пов-сть пластины, либо пошаговым экспонированием, при к-ром на пластину с определенным сдвигом (шагом) многократно проецируют фотошаблон с изображением одной структуры. Кроме фотолитографии используют также рентгеновскую и электронную литографию.

Для создания контактов вначале на пов-сти пластины (в маскирующем слое SiO2) формируют контактные окна, через к-рые затем напыляют металл, при этом образуются контактные площадки на периферии и соединит. дорожки между площадками и окнами; затем металл вжигают в пластины при 400-4500C в атмосфере H2.

По окончании формирования приборных структур пластины разделяют на отдельные кристаллы, разрезая их алмазным диском (наиб. часто) или др. способами. Кристаллы монтируют в корпус или на кристаллодержатель, после чего их контактные площадки соединяют (обычно ультразвуковой сваркой) с внеш. выводами на корпусе (кристалло-держателе) тонкими (10-30 мкм) проволочками из Al или Au.

Рассмотренные выше операции составляют основу планарной технологии дискретных полупроводниковых приборов. При создании интегральных схем возникают дополнит. проблемы, связанные с размещением большого числа взаимосвязанных компонентов на одном кристалле с огранич. площадью пов-сти. Для изоляции компонентов применяют два осн. способа: с помощью p-n-перехода, сформированного между компонентами, или слоя диэлектрика (SiO2); используют комбинацию этих способов.

Планарная технология разработана в 1959 в США. К кон. 80-х гг. она стала осн. технол. инструментом в произ-ве полупроводниковых приборов и интегральных схем.

Лит.: Мазель Е.З., Пресс Ф.П., Планарная технология кремниевых приборов, M., 1974; Малышева И. А., Технология производства микроэлектронных устройств, M., 1980; Пичугин И. Г., Таиров Ю.М., Технология полупроводниковых приборов, M., 1984; Технология СБИС, пер. с англ., кн. 1-2, M., 1986; Карбань В. И., Борзаков Ю. И., Обработка монокристаллов в микроэлектронике, M., 1988. Ф. П. Пресс.